#### Features

- Advanced, High-speed, Electrically-erasable Programmable Logic Device

- Superset of 22V10

- Enhanced Logic Flexibility

- Backward Compatible with ATV750B/BL and ATV750/L

- Low-power Edge-sensing "L" Option with 1 mA Standby Current

- D- or T-type Flip-flop

- Product Term or Direct Input Pin Clocking

- 7.5 ns Maximum Pin-to-pin Delay with 5V Operation

- Highest Density Programmable Logic Available in 24-pin Package

Advanced Electrically-erasable Technology

- Advanced Electrically-erasable lec

Reprogrammable

- Reprogramma

100% Tested

- Increased Logic Flexibility

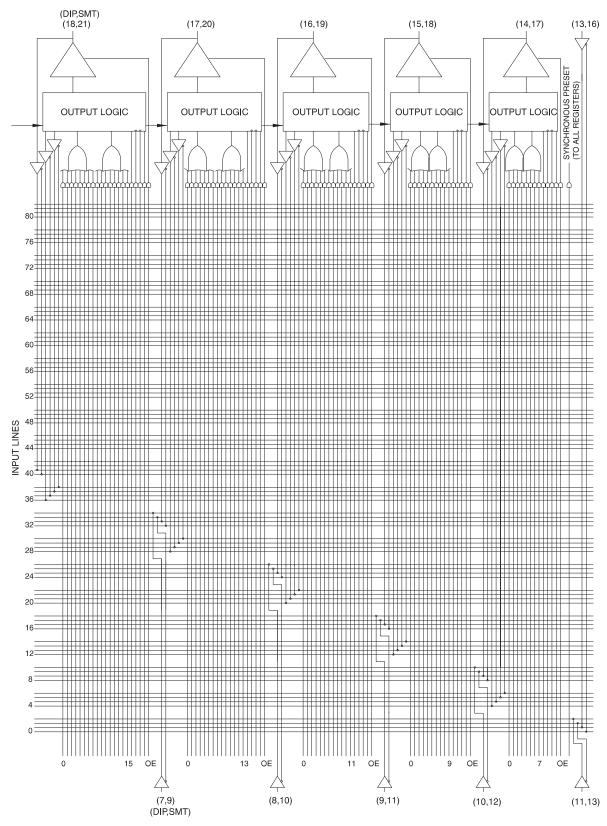

- 42 Array Inputs, 20 Sum Terms and 20 Flip-flops

- Enhanced Output Logic Flexibility

- All 20 Flip-flops Feed Back Internally

- 10 Flip-flops are also Available as Outputs

- Programmable Pin-keeper Circuits

- Dual-in-line and Surface Mount Package in Standard Pinouts

- Commercial and Industrial Temperature Ranges

- 20-year Data Retention

- 2000V ESD Protection

- 1000 Erase/Write Cycles

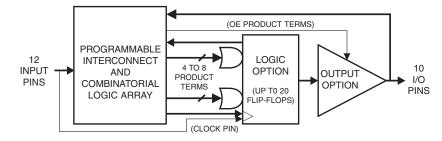

## **Block Diagram**

## Description

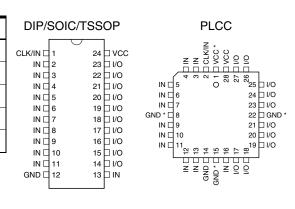

**Pin Name**

CLK

IN

I/O

GND

VCC

Note:

Pin Configurations

Function

Logic Inputs

+5V Supply

**Bi-directional Buffers**

For PLCC, pins 1, 8, 15, and 22

superior performance, connect VCC to pin 1 and GND to pins

can be left unconnected. For

Clock

Ground

8, 15, and 22.

The ATF750C(L)s are twice as powerful as most other 24-pin programmable logic devices. Increased product terms, sum terms, flip-flops and output logic configurations translate into more usable gates. High-speed logic and uniform predictable delays

#### (continued)

High-speed Complex Programmable Logic Device

## ATF750C ATF750CL

Rev. 0776H-03/01

guarantee fast in-system performance. The ATF750C(L) is a high-performance CMOS (electrically-erasable) complex programmable logic device (CPLD) that utilizes Atmel's proven electrically-erasable technology.

Each of the ATF750C(L)'s 22 logic pins can be used as an input. Ten of these can be used as inputs, outputs or bidirectional I/O pins. Each flip-flop is individually configurable as either D- or T-type. Each flip-flop output is fed back into the array independently. This allows burying of all the sum terms and flip-flops.

There are 171 total product terms available. There are two sum terms per output, providing added flexibility. A variable format is used to assign between four to eight product terms per sum term. Much more logic can be replaced by this device than by any other 24-pin PLD. With 20 sum

#### Absolute Maximum Ratings\*

| Temperature Under Bias55°C to +125°C                                       |

|----------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                          |

| Voltage on Any Pin with<br>Respect to Ground2.0V to +7.0V <sup>(1)</sup>   |

| Voltage on Input Pins<br>with Respect to Ground<br>During Programming      |

| Programming Voltage with<br>Respect to Ground2.0V to +14.0V <sup>(1)</sup> |

terms and flip-flops, complex state machines are easily implemented with logic to spare.

Product terms provide individual clocks and asynchronous resets for each flip-flop. Each flip-flop may also be individually configured to have direct input pin controlled clocking. Each output has its own enable product term. One product term provides a common synchronous preset for all flipflops. Register preload functions are provided to simplify testing. All registers automatically reset upon power-up.

The ATF750C(L) is a low-power device with speeds as fast as 15 ns. The ATF750C(L) provides the optimum low-power CPLD solution. This device significantly reduces total system power, thereby allowing batterypowered operations.

- \*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Note: 1. Minimum voltage is -0.6V DC, which may undershoot to -2.0V for pulses of less than 20 ns. Maximum output pin voltage is  $V_{CC}$  + 0.75V DC, which may overshoot to 7.0V for pulses of less than 20 ns.

### **DC and AC Operating Conditions**

All members of the family are specified to operate in either one of two voltage ranges. Parameters are specified as noted to be either 2.7V to 3.6V,  $5V \pm 5\%$  or  $5V \pm 10\%$ .

| 5V Operation                    | Commercial<br>-7.5, -10, -15 | Industrial<br>-10, -15 |

|---------------------------------|------------------------------|------------------------|

| Operating Temperature (Ambient) | 0°C - 70°C                   | -40°C - +85°C          |

| V <sub>CC</sub> Power Supply    | 5V ± 5%                      | 5V ± 10%               |

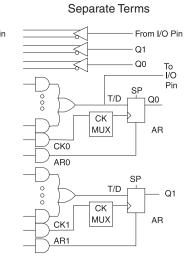

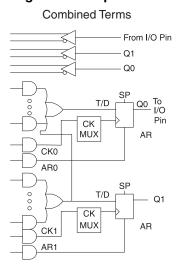

## **Logic Options**

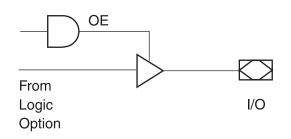

#### **Combinatorial Output**

**Combined Terms** From I/O Pin \$ Q1 ≲ Q0 To I/O Pin SP T/D Q0 СК MUX AR CK0 AR0 SP 000 T/D Q1 СК мих AR CK1 AR1

#### Registered Output

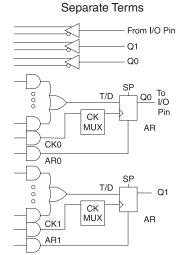

## **Clock Mux**

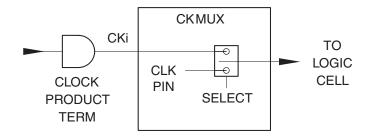

## **Output Options**

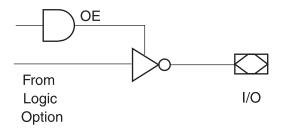

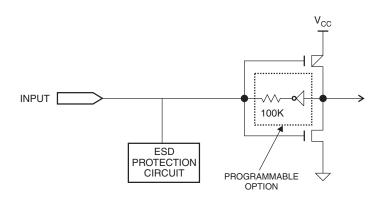

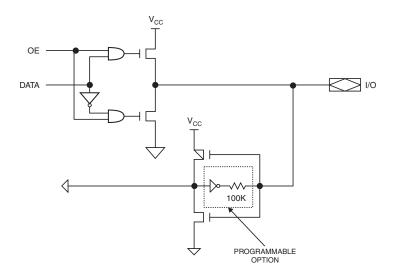

### **Bus-friendly Pin-keeper Input and I/Os**

All input and I/O pins on the ATF750C(L) have programmable "pin-keeper" circuits. If activated, when any pin is driven high or low and then subsequently left floating, it will stay at that previous high or low level.

This circuitry prevents unused input and I/O lines from floating to intermediate voltage levels, which causes unnecessary power consumption and system noise. The keeper circuits eliminate the need for external pull-up resistors and eliminate their DC power consumption.

Enabling or disabling of the pin-keeper circuits is controlled by the device type chosen in the logic compiler device selection menu. Please refer to the software compiler table for more details. Once the pin-keeper circuits are disabled, normal termination procedures are required for unused inputs and I/Os.

Table 1. Software Compiler Mode Selection

| Synario       | WINCUPL  | Pin-keeper Circuit |

|---------------|----------|--------------------|

| ATF750C       | V750C    | Disabled           |

| ATF750C (PPK) | V750CPPK | Enabled            |

#### **Input Diagram**

#### I/O Diagram

### **DC Characteristics**

| Symbol                         | Parameter                       | Condition                                               | on                        |            | Min  | Тур  | Max                    | Units |

|--------------------------------|---------------------------------|---------------------------------------------------------|---------------------------|------------|------|------|------------------------|-------|

| ILI                            | Input Load Current              | $V_{IN} = -0.1V$ to $V_{CC} + 1V$                       |                           |            |      |      | 10                     | μA    |

| I <sub>LO</sub>                | Output Leakage<br>Current       | $V_{OUT} = -0.1V$ to $V_{CC} + 0.1V$                    |                           |            |      |      | 10                     | μA    |

|                                |                                 |                                                         | 0.7.10                    | Com.       |      | 125  | 180                    | mA    |

|                                | C-7, -10                        | Ind., Mil.                                              |                           | 135        | 190  | mA   |                        |       |

|                                | Power Supply                    | V <sub>CC</sub> = Max,                                  | 0.45                      | Com.       |      | 125  | 180                    | mA    |

| Current, Standby               |                                 | C-15                                                    | Ind., Mil.                |            | 135  | 190  | mA                     |       |

|                                |                                 |                                                         | CL-15                     | Com.       |      | 0.12 | 1                      | mA    |

|                                |                                 |                                                         |                           | Ind., Mil. |      | 0.15 | 2                      | mA    |

| I <sub>OS</sub> <sup>(1)</sup> | Output Short<br>Circuit Current | $V_{OUT} = 0.5V$                                        | V <sub>OUT</sub> = 0.5V   |            |      |      | -120                   | mA    |

| V <sub>IL</sub>                | Input Low Voltage               | $4.5 \leq V_{CC} \leq 5.5 V$                            |                           |            | -0.6 |      | 0.8                    | V     |

| VIH                            | Input High Voltage              |                                                         |                           |            | 2.0  |      | V <sub>CC</sub> + 0.75 | V     |

|                                |                                 |                                                         | I <sub>OL</sub> = 16 mA   | Com., Ind. |      |      | 0.5                    | V     |

| V <sub>OL</sub>                | Output Low<br>Voltage           | $V_{IN} = V_{IH} \text{ or } V_{IL},$<br>$V_{CC} = Min$ | I <sub>OL</sub> = 12 mA   | Mil.       |      |      | 0.5                    | V     |

|                                | Voltage                         | v <sub>CC</sub> – with                                  | I <sub>OL</sub> = 24 mA   | Com.       |      |      | 0.8                    | V     |

| V <sub>OH</sub>                | Output High<br>Voltage          | $V_{IN} = V_{IH} \text{ or } V_{IL},$<br>$V_{CC} = Min$ | I <sub>OH</sub> = -4.0 mA |            | 2.4  |      |                        | V     |

Note: 1. Not more than one output at a time should be shorted. Duration of short circuit test should not exceed 30 sec.

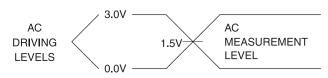

# Input Test Waveforms and Measurement Levels

t<sub>R</sub>, t<sub>F</sub> < 3 ns (10% to 90%)

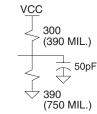

## **Output Test Load**

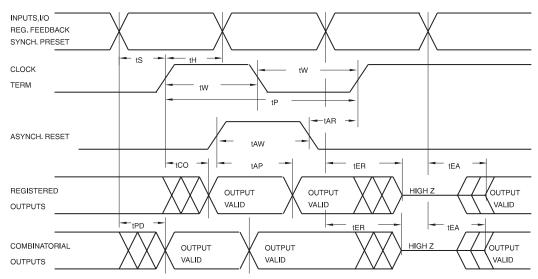

## AC Waveforms, Product Term Clock<sup>(1)</sup>

| Note: | 1.  | Timing measurement reference is 1.5V. Input AC driving levels are 0.0V and 3.0V, unless otherwise specified. |

|-------|-----|--------------------------------------------------------------------------------------------------------------|

| AC (  | Cha | racteristics, Product Term Clock <sup>(1)</sup>                                                              |

|                  |                                                          | -7  |     | -10 |     | C/CL-15 |       |       |

|------------------|----------------------------------------------------------|-----|-----|-----|-----|---------|-------|-------|

| Symbol           | Parameter                                                | Min | Max | Min | Max | Min     | Max   | Units |

| t <sub>PD</sub>  | Input or Feedback to Non-registered Output               |     | 7.5 |     | 10  |         | 15    | ns    |

| t <sub>EA</sub>  | Input to Output Enable                                   |     | 7.5 |     | 10  |         | 15    | ns    |

| t <sub>ER</sub>  | Input to Output Disable                                  |     | 7.5 |     | 10  |         | 15    | ns    |

| t <sub>co</sub>  | Clock to Output                                          | 3   | 7.5 | 4   | 10  | 5       | 12    | ns    |

| t <sub>CF</sub>  | Clock to Feedback                                        | 1   | 5   | 4   | 7.5 | 5       | 9     | ns    |

| t <sub>s</sub>   | Input Setup Time                                         | 3   |     | 4   |     | 8/12    |       | ns    |

| t <sub>SF</sub>  | Feedback Setup Time                                      | 3   |     | 4   |     | 7       |       | ns    |

| t <sub>H</sub>   | Hold Time                                                | 1   |     | 2   |     | 5       |       | ns    |

| t <sub>P</sub>   | Clock Period                                             | 7   |     | 11  |     | 14      |       | ns    |

| t <sub>w</sub>   | Clock Width                                              | 3.5 |     | 5.5 |     | 7       |       | ns    |

|                  | External Feedback 1/(t <sub>S</sub> + t <sub>CO</sub> )  |     | 95  |     | 71  |         | 50/41 | MHz   |

| f <sub>MAX</sub> | Internal Feedback 1/(t <sub>SF</sub> + t <sub>CF</sub> ) |     | 125 |     | 86  |         | 62    | MHz   |

|                  | No Feedback 1/(t <sub>P</sub> )                          |     | 142 |     | 90  |         | 71    | MHz   |

| t <sub>AW</sub>  | Asynchronous Reset Width                                 | 5   |     | 10  |     | 15      |       | ns    |

| t <sub>AR</sub>  | Asynchronous Reset Recovery Time                         | 3   |     | 10  |     | 15      |       | ns    |

| t <sub>AP</sub>  | Asynchronous Reset to Registered Output Reset            |     | 8   |     | 12  |         | 15    | ns    |

| t <sub>SP</sub>  | Setup Time, Synchronous Preset                           | 4   |     | 7   |     | 8       |       | ns    |

Note: 1. See ordering information for valid part numbers.

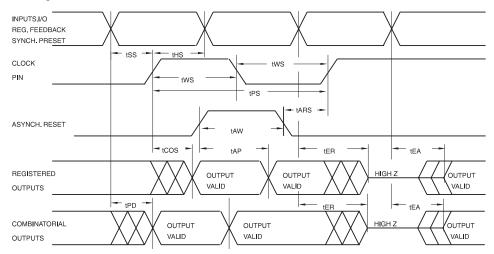

## AC Waveforms, Input Pin Clock<sup>(1)</sup>

Notes: 1. Timing measurement reference is 1.5V. Input AC driving levels are 0.0V and 3.0V, unless otherwise specified.

#### AC Characteristics, Input Pin Clock

|                   |                                                            | -   | 7   | -   | 10  | C/CL-15 |       |       |

|-------------------|------------------------------------------------------------|-----|-----|-----|-----|---------|-------|-------|

| Symbol            | Parameter                                                  | Min | Max | Min | Max | Min     | Max   | Units |

| t <sub>PD</sub>   | Input or Feedback to Non-registered Output                 |     | 7.5 |     | 10  |         | 15    | ns    |

| t <sub>EA</sub>   | Input to Output Enable                                     |     | 7.5 |     | 10  |         | 15    | ns    |

| t <sub>ER</sub>   | Input to Output Disable                                    |     | 7.5 |     | 10  |         | 15    | ns    |

| t <sub>cos</sub>  | Clock to Output                                            | 0   | 6.5 | 0   | 7   | 0       | 10    | ns    |

| t <sub>CFS</sub>  | Clock to Feedback                                          | 0   | 3.5 | 0   | 5   | 0       | 5.5   | ns    |

| t <sub>ss</sub>   | Input Setup Time                                           | 4   |     | 5   |     | 8/12.5  |       | ns    |

| t <sub>SFS</sub>  | Feedback Setup Time                                        | 4   |     | 5   |     | 7       |       | ns    |

| t <sub>HS</sub>   | Hold Time                                                  | 0   |     | 0   |     | 0       |       | ns    |

| t <sub>PS</sub>   | Clock Period                                               | 7   |     | 10  |     | 12      |       | ns    |

| t <sub>ws</sub>   | Clock Width                                                | 3.5 |     | 5   |     | 6       |       | ns    |

|                   | External Feedback 1/(t <sub>SS</sub> + t <sub>COS</sub> )  |     | 95  |     | 83  |         | 55/44 | MHz   |

| f <sub>MAXS</sub> | Internal Feedback 1/(t <sub>SFS</sub> + t <sub>CFS</sub> ) |     | 133 |     | 100 |         | 80    | MHz   |

|                   | No Feedback 1/(t <sub>PS</sub> )                           |     | 142 |     | 100 |         | 83    | MHz   |

| t <sub>AW</sub>   | Asynchronous Reset Width                                   | 5   |     | 10  |     | 15      |       | ns    |

| t <sub>ARS</sub>  | Asynchronous Reset Recovery Time                           | 5   |     | 10  |     | 15      |       | ns    |

| t <sub>AP</sub>   | Asynchronous Reset to Registered Output Reset              |     | 8   |     | 10  |         | 15    | ns    |

| t <sub>SPS</sub>  | Setup Time, Synchronous Preset                             | 5   |     | 5/9 |     | 11      |       | ns    |

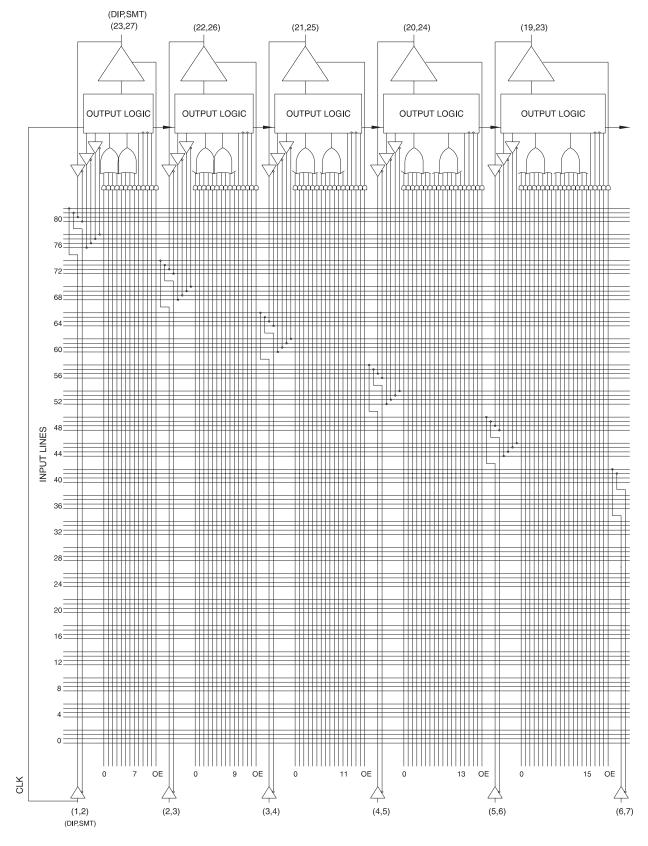

### Functional Logic Diagram ATF750C, Upper Half

ATF750C(L)

Functional Logic Diagram ATF750C, Lower Half

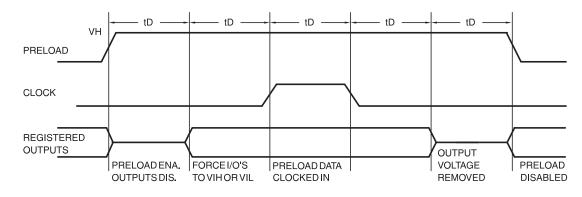

## Preload of Registered Outputs

The ATF750C(L)'s registers are provided with circuitry to allow loading of each register asynchronously with either a high or a low. This feature will simplify testing since any state can be forced into the registers to control test sequencing. A  $V_{\rm IH}$  level on the I/O pin will force the register

high; a  $V_{IL}$  will force it low, independent of the output polarity. The PRELOAD state is entered by placing a 10.25V to 10.75V signal on pin 8 on DIPs, and lead 10 on SMDs. When the clock term is pulsed high, the data on the I/O pins is placed into the register chosen by the select pin.

| Level Forced on Registered<br>Output Pin during Preload Cycle | Select Pin State | Register #0 State after Cycle | Register #1 State after Cycle |

|---------------------------------------------------------------|------------------|-------------------------------|-------------------------------|

| V <sub>IH</sub>                                               | Low              | High                          | Х                             |

| V <sub>IL</sub>                                               | Low              | Low                           | Х                             |

| V <sub>IH</sub>                                               | High             | Х                             | High                          |

| V <sub>IL</sub>                                               | High             | Х                             | Low                           |

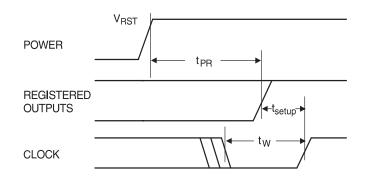

#### **Power-up Reset**

The registers in the ATF750C(L)s are designed to reset during power-up. At a point delayed slightly from  $V_{CC}$  crossing  $V_{RST}$ , all registers will be reset to the low state. The output state will depend on the polarity of the output buffer.

This feature is critical for state machine initialization. However, due to the asynchronous nature of reset and the uncertainty of how  $V_{CC}$  actually rises in the system, the following conditions are required:

- 1. The  $V_{CC}$  rise must be monotonic,

- 2. After reset occurs, all input and feedback setup times must be met before driving the clock terms or pin high, and

- The clock pin, or signals from which clock terms are derived, must remain stable during t<sub>PR</sub>.

| Parameter        | Description            | Тур | Max  | Units |

|------------------|------------------------|-----|------|-------|

| t <sub>PR</sub>  | Power-up Reset Time    | 600 | 1000 | ns    |

| V <sub>RST</sub> | Power-up Reset Voltage | 3.8 | 4.5  | V     |

### **Pin Capacitance**

$f = 1 \text{ MHz}, T = 25^{\circ}C^{(1)}$

|                  | Тур | Max | Units | Conditions           |

|------------------|-----|-----|-------|----------------------|

| C <sub>IN</sub>  | 5   | 8   | pF    | V <sub>IN</sub> = 0V |

| C <sub>OUT</sub> | 6   | 8   | pF    | $V_{OUT} = 0V$       |

Note: 1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

# Using the ATF750C's Many Advanced Features

The ATF750C(L)'s advanced flexibility packs more usable gates into 24 pins than any other logic device. The ATF750C(L)s start with the popular 22V10 architecture, and add several enhanced features:

- Selectable D- and T-type Registers Each ATF750C(L) flip-flop can be individually configured as either D- or T-type. Using the T-type configuration, JK and SR flip-flops are also easily created. These options allow more efficient product term usage.

- Selectable Asynchronous Clocks

Each of the ATF750C(L)'s flip-flops may be clocked by its own clock product term or directly from Pin 1 (SMD Lead 2). This removes the constraint that all registers must use the same clock. Buried state machines, counters and registers can all coexist in one device while running on separate clocks. Individual flip-flop clock source selection further allows mixing higher performance pin clocking and flexible product term clocking within one design.

- A Full Bank of Ten More Registers

The ATF750C(L) provides two flip-flops per output logic cell for a total of 20. Each register has its own sum term, its own reset term and its own clock term.

- Independent I/O Pin and Feedback Paths Each I/O pin on the ATF750C(L) has a dedicated input path. Each of the 20 registers has its own feedback terms into the array as well. This feature, combined with individual product terms for each I/O's output enable, facilitates true bi-directional I/O design.

# Synchronous Preset and Asynchronous Reset

One synchronous preset line is provided for all 20 registers in the ATF750C(L). The appropriate input signals to cause the internal clocks to go to a high state must be received during a synchronous preset. Appropriate setup and hold times must be met, as shown in the switching waveform diagram.

An individual asynchronous reset line is provided for each of the 20 flip-flops. Both master and slave halves of the flipflops are reset when the input signals received force the internal resets high.

## Security Fuse Usage

A single fuse is provided to prevent unauthorized copying of the ATF750C(L) fuse patterns. Once the security fuse is programmed, all fuses will appear programmed during verify.

The security fuse should be programmed last, as its effect is immediate.

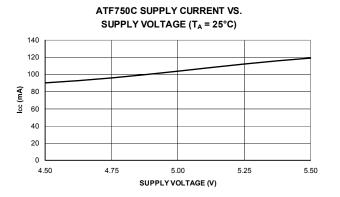

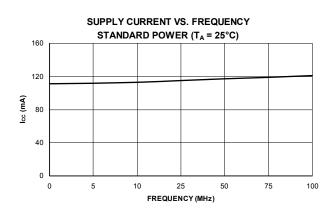

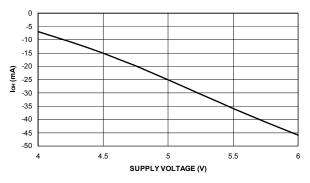

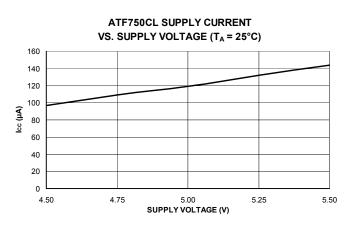

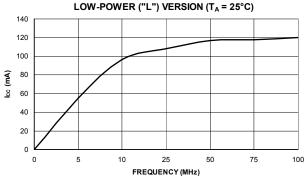

SUPPLY CURRENT VS. FREQUENCY

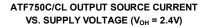

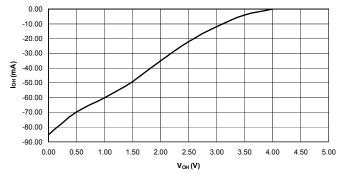

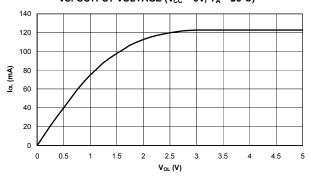

ATF750C/CL OUTPUT SOURCE CURRENT VS. OUTPUT VOLTAGE ( $V_{CC}$  = 5V,  $T_A$  = 25°C)

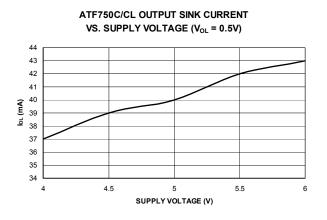

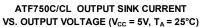

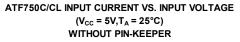

ATF750C/CL OUTPUT SINK CURRENT VS. OUTPUT VOLTAGE (V\_{CC} = 5V, T\_A = 25°C)

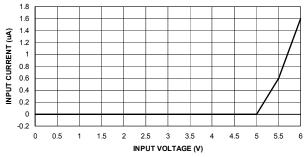

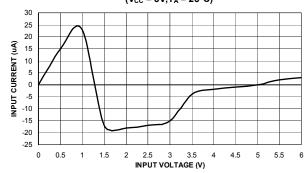

ATF750C/CL INPUT CURRENT VS. INPUT VOLTAGE  $(V_{CC}=5V, T_A=25^\circ\text{C})$

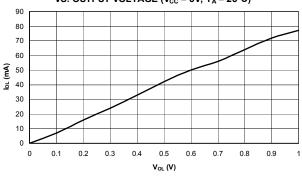

ATF750C/CL INPUT CLAMP CURRENT VS. INPUT VOLTAGE ( $V_{CC} = 5V, T_A = 35^{\circ}C$ )

### ATF750C(L) Ordering Information

| t <sub>PD</sub><br>(ns) | t <sub>cos</sub><br>(ns) | Ext.<br>f <sub>MAXS</sub><br>(MHz) | Ordering Code                                                                   | Package                                  | Operation Range               |

|-------------------------|--------------------------|------------------------------------|---------------------------------------------------------------------------------|------------------------------------------|-------------------------------|

| 7.5                     | 6.5                      | 95                                 | ATF750C-7JC                                                                     | 28J                                      | Commercial<br>(0°C to 70°C)   |

| 10                      | 7                        | 83                                 | ATF750C-10JC<br>ATF750C-10PC<br>ATF750C-10SC<br>ATF750C-10XC <sup>(1)</sup>     | 28J<br>24P3<br>24S<br>24X <sup>(1)</sup> | Commercial<br>(0°C to 70°C)   |

|                         |                          |                                    | ATF750C-10JI<br>ATF750C-10PI<br>ATF750C-10SI                                    | 28J<br>24P3<br>24S                       | Industrial<br>(-40°C to 85°C) |

| 15                      | 10                       | 55                                 | ATF750C-15JC<br>ATF750C-15PC<br>ATF750C-15SC<br>ATF750C-15XC <sup>(1)</sup>     | 28J<br>24P3<br>24S<br>24X <sup>(1)</sup> | Commercial<br>(0°C to 70°C)   |

|                         |                          | -                                  | ATF750C-15JI<br>ATF750C-15PI<br>ATF750C-15SI                                    | 28J<br>24P3<br>24S                       | Industrial<br>(-40°C to 85°C) |

| 15                      | 10                       | 44                                 | ATF750CL-15JC<br>ATF750CL-15PC<br>ATF750CL-15SC<br>ATF750CL-15XC <sup>(1)</sup> | 28J<br>24P3<br>24S<br>24X <sup>(1)</sup> | Commercial<br>(0°C to 70°C)   |

|                         |                          |                                    | ATF750CL-15JI<br>ATF750CL-15PI<br>ATF750CL-15SI                                 | 28J<br>24P3<br>24S                       | Industrial<br>(-40°C to 85°C) |

Note: 1. Special order only: TSSOP package requires special thermal management.

## Using "C" Product for Industrial

To use commercial product for industrial ranges, down-grade one speed grade from the "I" to the "C" device (7 ns "C" = 10 ns "I") and de-rate power by 30%.

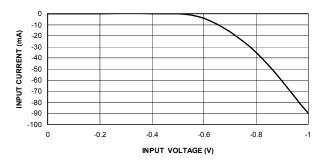

|                           | Package Type                                                 |  |  |  |  |

|---------------------------|--------------------------------------------------------------|--|--|--|--|

| 28J                       | 28-lead, Plastic J-leaded Chip Carrier (PLCC)                |  |  |  |  |

| 24P3                      | 24-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)     |  |  |  |  |

| 24S                       | 24-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC) |  |  |  |  |

| <b>24X</b> <sup>(1)</sup> | 24-lead, 0.173" Wide, Thin Shrink Small Outline (TSSOP)      |  |  |  |  |

### **Packaging Information**

ATF750C(L)

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel U.K., Ltd. Coliseum Business Centre Riverside Way Camberley, Surrey GU15 3YL England TEL (44) 1276-686-677 FAX (44) 1276-686-697

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

Atmel Rousset Zone Industrielle 13106 Rousset Cedex France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

#### Atmel Smart Card ICs Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

#### *Fax-on-Demand* North America: 1-(800) 292-8635 International: 1-(408) 441-0732

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

*BBS* 1-(408) 436-4309

#### © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Marks bearing <sup>®</sup> and/or <sup>™</sup> are registered trademarks and trademarks of Atmel Corporation.

Terms and product names in this document may be trademarks of others.